Electronic Circuit Design : How To Reduce The Probability Of "Metastability"?

Metastability and design reliability

When designing a digital circuit, it is important to know that synchronization is important, especially when you want to enter a signal into a synchronous circuit, but when the signal is driven by another clock, it is something that needs to be done at the interface to make the incoming asynchronous signal Synchronization, otherwise the circuit will not work, because the input is likely to appear Metastability (Metastability), resulting in sampling error.

Below we will do some introduction to the principle of metastability, causes, hazards, solutions, the impact on reliability and elimination of the simulation.

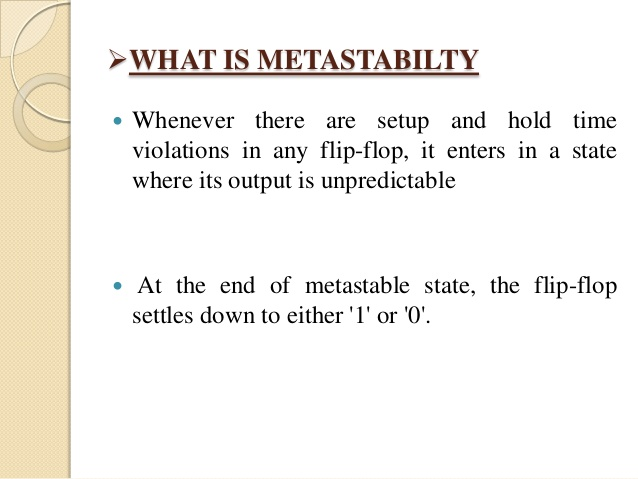

What is metastability?

source

Metastability refers to the trigger can not reach a confirmed state within a specified period of time. When a flip-flop is metastable, it can neither predict the unit's output level nor predict when the output will stabilize at the correct level. During this settling period, the flip-flop outputs some intermediate level or may be oscillating and this useless output level can be cascaded along the various flip-flops on the signal path.

Metastablity causes

In a synchronous system, if the setup time / hold time of the flip-flop is not satisfied, metastability may occur. At this time, the output Q of the flip-flop is in an indefinite state for a relatively long time after the valid clock edge. During this period Q end glitch time, oscillation, a fixed voltage value, rather than equal to the value of the data input D. This period of time between the resolution (resolution time). Q after the resolution time will be stabilized to 0 or 1, but whether it is 0 or 1, which is random, and the input is not necessarily related.

Metastability hazards

Since the output may be glitch, oscillating, fixed voltage values before stabilizing, the metastable state, in addition to causing logical false positives, will output a metastable intermediate level between 0 and 1 State (ie, causing metastable state). Logical misjudgments have the potential to mitigate the hazard through the circuit's special design (such as the role of the Gray code counter in an asynchronous FIFO), while metastable propagation expands the fault plane and makes it difficult to handle.

Metastablity solution

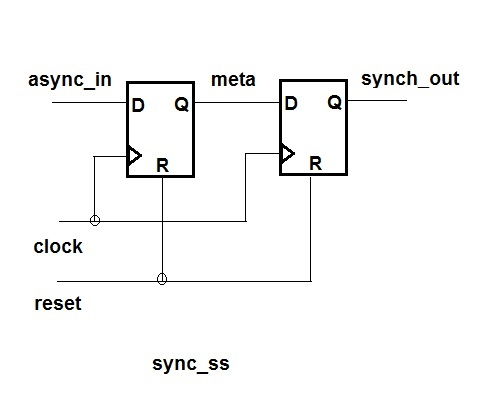

As long as there are asynchronous components in the system, metastability is unavoidable. Therefore, the designed circuit must first reduce the occurrence of errors caused by metastability, and secondly, make the system insensitive to errors. The former to achieve synchronization, while the latter according to different design and application of different approaches. A typical circuit that uses synchronization to reduce the chance of metastability is shown in Figure 1.

Figure 1 two-stage synchronization circuit

source

In Figure 1, the left is the asynchronous input, after two-stage trigger synchronization, the output on the right will be synchronized, and the output is basically no metastability. The principle is that even if the output of the first flip-flop is metastable, the probability that the level of the second flip-flop D is still unstable after a period of CLK is negligible so that the Q terminal of the second flip-flop is essentially not Metastable will produce. Note that here is the "basic", that is, can not be "eradicated", then if the second flip-flop Q metastable there any consequences?

The severity of the consequences depends on your design. If the system is not sensitive to errors, the system may work properly or resume normal operation after a short period of exception. For example, when designing an asynchronous FIFO, use the Gray code counter to read and write Address pointer is in this regard. If design is not designed to reduce the sensitivity of the system to metastability, the system may collapse in the event of metastability.

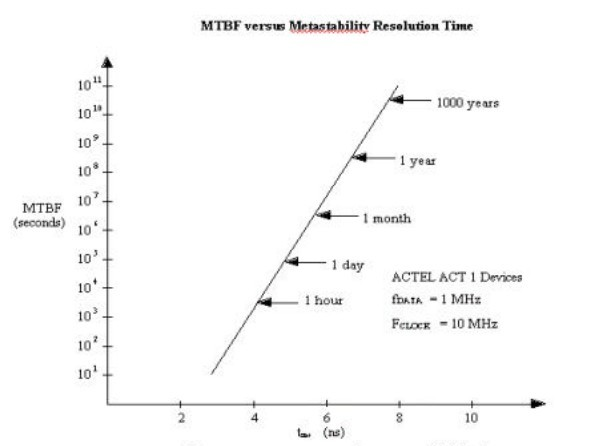

Metastability and system feasibility

After the use of synchronous circuits, metastable state still may occur, which is connected with the Mean Time Between Failure (MTBF), the probability of occurrence of metastability and the clock frequency has nothing to do, but the MTBF and the clock are closely related. An article provides an example where a system operating at 20 MHz clocks has an MTBF of about 50 years, but with a clock frequency raised to 40 MHz, the MTBF is only 1 minute! It can be seen that reducing the clock frequency can greatly reduce the occurrence of system errors caused by metastability. The reason for this is that providing longer resolution time can reduce the chance of metastable state transmission to the next stage and increase the MTBF of the system, as shown in FIG. 2 Show.

Figure 2 resolution time and MTBF relationship

Conclusions

Metastability and design reliability are closely related. At present, for many designs, it is not difficult to realize the required functions. The difficulty is to improve the stability and reliability of the system and the probability of smaller metastability. Reducing the system's sensitivity to metastable errors can improve system reliability.

References used for Text and Images:

- https://daffy1108.wordpress.com/2014/06/08/synchronizers-for-asynchronous-signals/

- https://www.slideshare.net/prashantsingh94651/mtbf

- https://en.wikipedia.org/wiki/Metastability_(electronics)

- https://resources.altium.com/pcb-design-blog/reducing-metastability-in-fpga-designs

- https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/wp/wp-01082-quartus-ii-metastability.pdf

- http://vlsihomepage.com/2007/09/03/metastability-in-design/

Support @steemstem and the #steemstem

project - curating and supporting quality STEM

related content on Steemit

This post has received a 0.05 % upvote from @drotto thanks to: @amity123.

This post has received a 1.10% upvote from thanks to: @amity123.

thanks to: @amity123.

For more information, click here!!!!

Send minimum 0.050 SBD/STEEM to bid for votes.

Do you know, you can also earn daily passive income simply by delegating your Steem Power to @minnowhelper by clicking following links: 10SP, 100SP, 500SP, 1000SP or Another amount

You have collected your daily Power Up! This post received an upvote worth of 1.71$.

Learn how to Power Up Smart here!

Greetings! I am a minnow exclusive bot that gives a 5X upvote! I recommend this amazing guide on how to be a steemit rockstar! I was made by @EarthNation to make Steemit easier and more rewarding for minnows.