CPCI外围槽适配器设计思路

CPCI外围槽适配器设计思路

CPCI系统槽适配器可以看成计算机的PCI接口,而外围设备可以看成插在计算机上的板卡。

其实我一度疑惑,背板前后都可以插CPCI插座,而背板一般设计厚度是3.2mm,一个CPCI插座插进去在另一面就会透出针来,那背面的插座该怎么插进去呢?原来这时一个CPCI的插座得选择长针的(16mm),一面只是个针套,直接套在透过去的针上就行了。

一般来说一个CPCI板卡3U的尺寸为100mm×160mm,而6U的尺寸为233.35mm×160mm。

连接器常用的是A型,B型,AB型。每种类型为阴阳一对,A型用于J1/P1和J4/P4,板卡上的为阴连接器,底板上为阳连接器。

板卡上的连接器有接地屏蔽罩(F列),此屏蔽罩为背板逻辑地提供地阻抗回路。B22型(B型的一种)用于J2/J5连接器,J3是B19型连接器。底板后插连接器准确的说是护壳,叫AB22或B22型护壳。但是后插板rJ2/rJ5是AB22型阴连接器。

适配器电源及电源引脚应该具备退耦需求。一般使用0.1F+10uF的电容。

信号端接。适配器卡上的很多PCI信号需要在连接器处端结10Ω电阻,可以使用排阻。这些信号包括AD[31:0],C/BE[3:0]#,PAR,FRAME#,IRDY#,TRDY#,STOP#,LOCK#,IDSEL,DEVSEL#,PERR#,SERR#,RST#。除此之外,如果以下信号被使用的话,也需要端接。INTA#,INTB#,INTC#,INTD#,AD[63:32],C/BE[7:4]#,REQ64#,ACK64#,PAR64。REQ#需要在驱动端端接电阻,但我看有些设计也没有太讲究,还是在接口处端接。

对于需要端接的信号,要求包含电阻在内的走线长度不大于2500mil,并且需要控制走线阻抗为65Ω±10%。外围槽适配器一个PCI信号只能挂一个负载,也就是只能与一个PCI板卡相连,但33MHz系统槽适配器可以挂两个。关于系统槽适配器这里不多做介绍。

外围适配器时钟信号长度应为2500mil±100mil。

上拉定位。5V上拉采用1kΩ,3.3V上拉采样2.7kΩ。上拉电阻的端接长度包含电阻在内要小于500mil。

对于GNT#信号要连接一个100kΩ的上拉电阻。

如果外围适配器时钟频率是66MHz,时钟信号的长度应为2500mil±40mil。且为了补偿时钟延迟,要求使用内层带状线架构。

适配器前面板为金属外壳,需要与机壳地相连。同时,适配板需要有ESD静电导出条,为3段。第一段通过10MΩ与第三段相连,第二段通过10MΩ接逻辑地。第三段直接通过螺钉接到前面板上。其中第一段长40mm,宽1.5mm,距板边1mm(长)和0.5mm(短斜)。第一段和第二段距20mm,第二段长55mm,宽1.5mm,与第三段间距5mm。第三段与前面板底边安装孔相连,长32.4mm,宽1.5mm。前面板安装孔尺寸为7.6mm(长)×8.4mm(宽),弧度为半径2.5mm。TOP和BOTTOM面都要有,并且通过通孔互联。10MΩ电阻控制静电泄放速度,因为静电泄放太快易引起电火花。

前面板应该有三角形或圆形来表示此板卡是系统板卡还是外围适配器。机箱上的系统槽可以用红色指示幅来指示。

CPCI J2用作IO,类似于单片机的IO。功能由用户自定义,同时通过后插板实现信号调理,信号变换,物理寻址等功能。P2上的GA[4:0]用于槽位地址唯一编码,需要上拉。实际上类似于这样的信号,可以上拉,并连接FPGA IO引脚进行读取。

后插板可以是3U,也可以是6U。但长度是标准的80mm,为前插板的一半。

这里仅介绍CPCI适配器PCI总线部分,至于本地总线就涉及桥接芯片的事了。这里也未涉及系统槽适配器的事。

总结下来32bit CPCI接口PCI信号差不多50个信号加上GA[4:0]就是55个信号。

[WhereIn Android] (http://www.wherein.io)

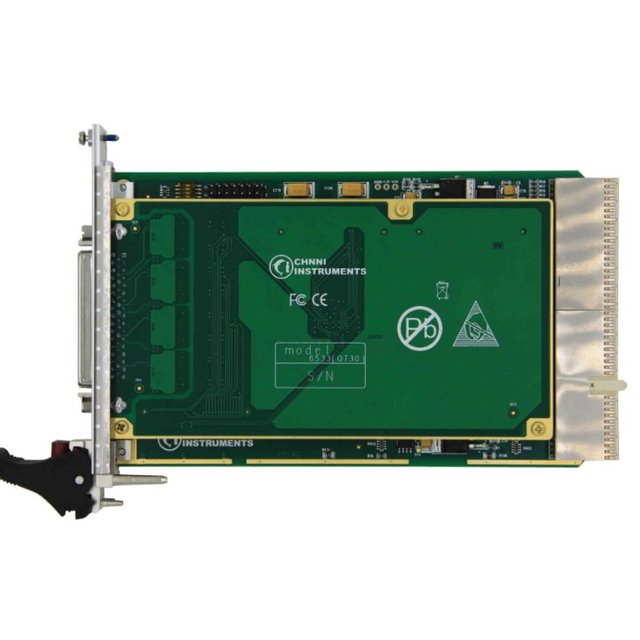

看起来好像显卡!shop

[WhereIn Android] (http://www.wherein.io)

不是显卡,是采集卡,显卡更复杂

[WhereIn Android] (http://www.wherein.io)

你好鸭,lucienyong!

@boylikegirl给您叫了一份外卖!

新手村和平鸽子

吃饱了吗?跟我猜拳吧! 石头,剪刀,布~

如果您对我的服务满意,请不要吝啬您的点赞~

老哥的这个文章专业知识太强 我有点头晕😵了

[WhereIn Android] (http://www.wherein.io)

😅😛

[WhereIn Android] (http://www.wherein.io)

This post has been rewarded by the Steem Community Curation Project #wherein

昨天明明把手机放在桌上,今天又找不到了 ( ˘︹˘ )

咦?你是谁?我又是谁?

加入我们微信群没?还没的话赶快加我们瓜子老板。很帅的 iguozi <(^,^)>

Ha recibido un voto a favor de la comunidad WHEREIN, impulsada por STEEMIT INC. Gracias por usar WHEREIN

Terimakasih Sudah Menggunakan WhereIn, Postingan Anda Terpilih Untuk Mendapatkan Upvote Dari WhereIn Dan Di Dukung Oleh Steemit.inc !

我重新检查了一下,对于CPCI A列的A2 TCK引脚,A4引脚IPMB_PWR和A5引脚BRSVP1A5设计中或许会悬空,因为外围适配器没用JTAG,电源管理和SDONE#信号。但是背板对于这些信号未必没做处理,我记得是各槽间共享连接了。

[WhereIn Android] (http://www.wherein.io)

桥接芯片PCI9054有一个PME#管脚,一般悬空。但有时我想如果要使用它,该接到CPCI哪个引脚好呢?

[WhereIn Android] (http://www.wherein.io)

对于B列,B3是PCI中断INTB#,由于一个外围适配器只用了一个PCI中断INTA#,所以此引脚就悬空;对于B4,Healthy#,母板每个槽分别借一个电容到地,外围槽是直接接地了。B5,BRSVP1B5,由于不使用SBO#,同样悬空;B17,IPMB_SCL,外围槽未用到此功能,悬空;B25,REQ64#,外围槽悬空,其余信号符合CPCI J1信号定义。

[WhereIn Android] (http://www.wherein.io)

healthy#“外围槽是直接接地了”改成“外围槽适配器是直接接地了”

[WhereIn Android] (http://www.wherein.io)

对于C列,以下引脚悬空,C1,TRST#,C2,TMS,C3,INTC#,C17,IPMB_SDA,C25,ENUM#,其余引脚与CPCI J1定义一致

[WhereIn Android] (http://www.wherein.io)

其实PCI9054有一个ENUM#引脚,不过有时并不会引到CPCI上,只是电路上对此引脚进行10k上拉。

[WhereIn Android] (http://www.wherein.io)

关于D列,D4 INTP悬空,D21 M66EN悬空。D2 TDO与E2 TDI连在一起。D6为PCLK输入,即PCI时钟输入。D15,BD_SEL#引脚接地。

[WhereIn Android] (http://www.wherein.io)

这个PCLK一般作为桥接芯片的时钟输入,比如PCI9054。

[WhereIn Android] (http://www.wherein.io)

对于E列,E3 INTD#悬空,E4 INTS悬空,E24 ACK64#悬空。其余信号与CPCI J2信号定义一致。

[WhereIn Android] (http://www.wherein.io)

其实对于32位系统,J2应依照后面板IO连接器引脚分配

[WhereIn Android] (http://www.wherein.io)