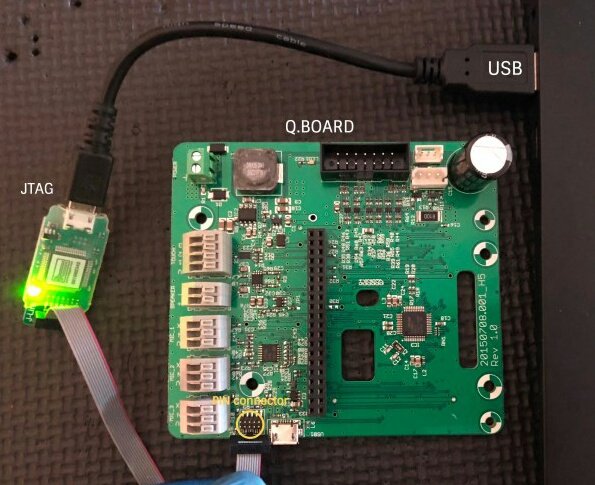

JTAG

JTAG(IEEE 1149.1, Joint Test Action Group ) industry standard interface for testing and debugging.

Ex: System level testing, Serial boundary-scanning, Low-level testing of dies and components, Firmware debugging (single stepping and setting Breakpoints)

It can provide a direct interface to hardware.

Ex: Flash memory programming

CONNECTIONS

5 connections(4required, 1optional)

TDO-> (Test Data Output) outputs data which comes from the test data registers or instruction register.

TDI-> (Test Data Input) receives input data which is feed to the test data registers or instruction register.

TMS-> (Test Mode Select Input) controls the operation of the test logic, by receiving the incoming data.

TCK-> (Test Clock) has noting to do with the board or system clock. The Test Clock is used to load the test mode data from the TMS pin, and the test data on the TDI pin.

TRST-> (Test Rest)resets the JTAG test logic.

-Many development environments provide support for JTAG interface.

-Low level functionality is abstracted from the user.

-Some open-source S/W tools exist.

Ex: Open On-Chip Debugger (Open OCD).

Removing JTAG functionality from a device is difficult.

-inconvenient because it would remove programming |debug| testing capabilities for the legitimate users. Maybe password protected