생생한 반도체 이야기 – 미세패터닝 기술의 한계를 넘는 더블 패터닝 기술(1)

안녕하세요, capincau입니다.

지난 번에 E-UV에 관한 이야기를 간단하게 했습니다. PHOTO 공정을 잠시 살펴보았고 PHOTO 공정은 광원의 파장이 짧을수록 해상력이 좋아져서 미세패턴을 구현하는 것이 유리한데, E-UV를 광원으로 사용하면 10nm 이하의 미세패턴이 가능해진다고 정리할 수 있겠습니다.

한 가지 특이한 것이 광원에 따른 파장의 변화인데, g-LINE(436nm), i-LINE(365nm), KrF(248nm), ArF(193nm), E-UV(13.5nm)로 넘어가는 과정 중 ArF와 E-UV의 간격이 엄청나다는 것이 눈에 띕니다. 과연 그 사이에는 무엇이 있었을까요?

반도체의 패터닝 기술

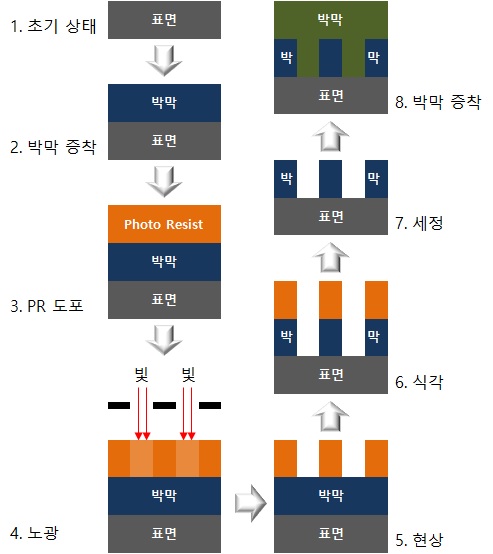

반도체의 패터닝 기술은 박막증착, PR도포, 노광 및 현상, 식각, 세정, 박막증착의 단위 공정을 필요한 만큼 반복하는 것을 기본으로 하고 있습니다. 전기적인 특성을 결정하는 이온주입과 열처리, 그리고 평탄화를 위한 연마 공정 등이 추가되기도 합니다. 가장 단순한 반도체의 패터닝 방법은 그림 1과 같이 표현할 수 있습니다.

그림 1 – 반도체의 패터닝 방법

‘무어의 법칙’을 들어본 적이 있을 겁니다. 반도체의 성능은 18개월을 주기로 두 배 증가한다는 것인데요, 1965년에 인텔의 공동 설립자 중 한 사람인 고든 무어가 반도체 기술의 발전속도를 표현한 것으로 널리 알려져 있습니다. 여기서 반도체의 성능은 메모리의 용량과 CPU의 속도를 의미하는데 반도체의 성능, 특히 메모리의 용량을 증가시키는데 미세 패터닝 기술은 절대적입니다. 동일한 면적에 용량을 늘리려면 더 많은 반도체 소자를 넣어야 하고, 이것이 가능하려면 반도체 소자를 더 작게 만들어야 하니까요. 물론 3D NAND와 같이 위로 쌓아 올려서 용량을 증가시킨 제품도 있습니다만, 여전히 2D 구조의 반도체 소자가 기본인 DRAM은 미세 패터닝 기술이 아니면 같은 크기의 메모리 칩에 용량을 늘릴 수 있는 방법이 없습니다.

PR MASK의 한계

미세 패터닝 기술을 이야기할 때 우리는 디자인 룰(design rule, DR)이라는 용어를 사용합니다. 반도체는 좁은 공간에 엄청나게 많은 수의 트랜지스터가 들어가 있습니다. 트랜지스터를 동작시키기 위해서 GATE에 전압을 인가하는데, GATE와 GATE 간의 거리를 DR이라고 합니다. 현재 양산에서 사용하는 PHOTO 공정의 광원 중 가장 미세한 패턴을 만들 수 있는 것은 ArF입니다. 일반적으로 ArF는 DR 40nm까지 패터닝이 가능합니다. 알려져 있는 것처럼, 메모리 1위인 삼성전자와 시스템 반도체 1위인 TSMC는 10nm급의 제품을 생산하고 있습니다. ArF의 미세 패터닝 공정능력은 40nm까지 가능한데 삼성전자와 TSMC의 두 업체는 어떻게 10nm 급 제품을 생산할 수 있을까요?

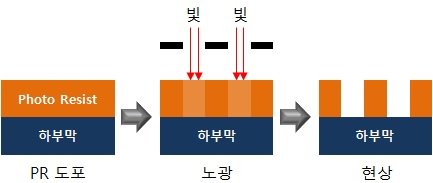

40nm 이하 미세 패터닝의 기술은 더블 패터닝 기술(Double Patterning Technology, DPT)에 의해 구현이 되었습니다. 말 그대로 double, 즉 두 배가 된다는 의미입니다. DPT라는 공정기술을 설명하기에 앞서, 지난 번에 소개했던 PHOTO 공정을 다시 한번 불러 오겠습니다. PHOTO 공정은 PR이라고 하는 소재를 이용하여 제거해야 할 부분은 PR을 제거하고 남겨야 할 부분은 PR을 남겨두는 공정이라고 간단하게 설명할 수 있습니다. 가장 널리 사용되는 positive PR을 이용한 PHOTO 공정을 그림 2와 같이 표현하였습니다.

그림 2 – positive PR을 이용한 PHOTO 공정

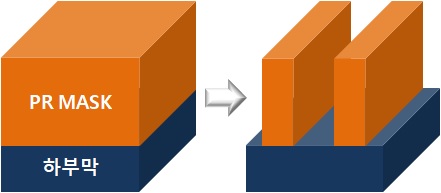

위의 그림은 패턴의 단면을 그린 것입니다. 최종 결과를 입체로 나타내면 그림 3과 같이 표현할 수 있습니다.

.jpg)

그림 3 – 현상 후 PR의 입체적인 모습

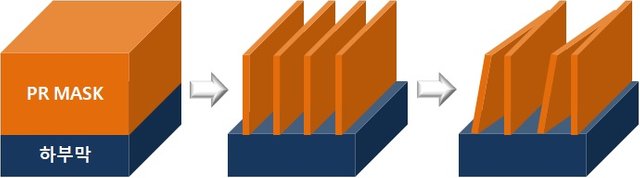

여기서 미세패턴을 만들려면 PR이 어떤 형태가 되어야 할까요? 높이는 그대로 두고 PR의 폭이 점점 좁아져야 할 겁니다. 그리고 하부막 위에 남은 PR의 간격이 점점 가까워지겠지요. 그림 4의 가운데와 같이 표현할 수 있습니다.

그림 4 – 미세패턴일 때 현상 후 남은 PR과 쓰러진 상태

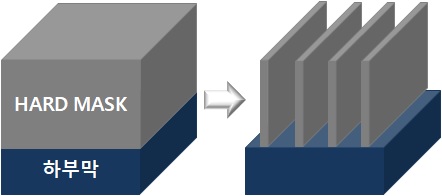

PR이 그림 4와 같은 형태를 잘 유지해 준다면 아무런 문제가 없겠지만, 현실은 그렇지 못합니다. 가로에 대한 세로의 비율(aspect ratio라고 합니다)이 특정값보다 커지게 되면 PR은 서있지 못하고 쓰러지기 때문에 dry etch 후 정상적인 패턴을 얻기 어려워집니다. 그래서 현재의 제품들은 PR을 MASK로 사용하지 않고 동일한 CARBON 성분의 HARD MASK를 사용합니다. HARD MASK에는 DLC라든지 SOH와 같은 막질이 있는데, 다음에 한번 다뤄보겠습니다. HARD MASK는 PR을 대체한다고만 이해해 두시면 되고, 패터닝이 끝난 HARD MASK는 그림 5와 같이 나타낼 수 있습니다.

그림 5 – 패터닝이 끝난 HARD MASK

마무리

자, 여기까지 잘 이해하셨는지 모르겠네요. 이번 이야기를 준비하면서 DPT가 어떻게 구현되는지 설명하는 것을 목표로 하였습니다만, 왜 DPT가 필요한 지 설명하는 것만 해도 글이 꽤 길어졌네요. DPT를 설명할 때 HARD MASK를 빼놓을 수가 없기 때문에 HARD MASK를 다음 번에 소개하고 그 후에 DPT를 구현하는 방법을 다룰까 합니다. 긴 글 읽어주셔서 고맙습니다.

참고자료

반도체 공정용 리소그래피 기술의 최근 동향 https://ettrends.etri.re.kr/ettrends/53/0905000077/

포토레지스트 기술동향 http://www.kipo.go.kr/club/file.do?attachmentId=7709