CPCI母板设计

CPCI母板设计

以前做过CPCI总线的总结,不过现在看来就觉得过于表面,而且没有条理。所以打算对CPCI重新做一下总结,并且以硬件或软件协议不同方向进行描述,同时硬件又分为母板和适配器两个方面。

CPCI母板其实就是插CPCI板卡的底板。考虑到系统时钟频率分为33MHz和66MHz两种情况,所以一个母板所容纳的CPCI的插槽的数量是不同的。时钟频率为33MHz的母板所容纳的插槽数量是8个,1个系统板和7个外围板卡。时钟为66MHz时最多5个插槽。槽与槽之间的间距为800mil。一般系统槽在最左边或最右边。

系统槽可以为总线上所有的适配器提供仲裁,时钟分配以及复位功能。

说到插槽就不得不说,CPCI使用的连接器。CPCI使用的是2mm间距5行的连接器。一般3U的安装J1和J2两种,6U的安装J1,J2,J3,J4,J5。

背板应当提供相互分离的3.3V,5V电源平面和接地面。V(I/O)应当占用一个单独的电源平面。

背板的CPCI信号线应当通过叠层和走线做阻抗控制。阻抗应当被控制在65Ω±10%。

对于上拉到V(I/O)的信号线,都需要在远离系统槽的地方添加快速肖特基端接。

V(I/O)是配置成5V还是3.3V,取决于实际需要。早先好像默认配置成5V,但现在很多板子默认都是3.3V。

系统槽的IDSEL信号接地,外围槽IDSEL信号需要分别接到AD31~AD25信号引脚上。

系统槽需要提供7对REQx#/GNTx#信号给外围槽。

对于信号INTA#,INTB#,INTC#,INTD#采样循环式中断。即系统槽信号顺序是ABCD,外围槽1则应该是DABC,外围槽2就是CDAB,外围槽3则是BCDA,外围槽4重新变为ABCD。这里指的是引脚信号连接顺序。从软件上来说称为BIOS中断绑定。

另外可以使用PRST#信号对系统槽适配器重启,系统槽适配器再通过RST#信号重启其它设备。系统槽适配器应对此信号用一个1kΩ的电阻上拉。可以通过DEG#和FAL#信号反映系统供电状态,需要系统槽适配器对这两个信号用1kΩ电阻上拉。

系统通过SYSEN#信号来判断是不是系统槽。系统槽将此信号接地,外围槽将此信号悬空,并且外围槽适配器需要用电阻将此信号上拉至V(I/O)。

另外INTP是非PCI中断,可用作控制中断,可发送给系统主设备上的任意继起ISA中断。系统槽适配器需要将此信号通过电阻上拉至V(I/O)。

至于INTS则是符合PCI串行系统IRQ规范的串行中断。系统槽适配器需要将此信号通过上拉电阻拉至V(I/O)。

还有一个信号是ENUM#,这个信号是支持热插拔的板卡插拔之后产生的信号,系统识别这个信号后一般会进行软件处理,这个信号的使用具体参考CPCI热插拔规范。不过,系统槽适配器一般应将此信号上拉。

GA[4:0]是为了能够唯一的识别P2槽所用一组物理寻址信号。一般适配器通过将此信号通过10kΩ±10%的电阻进行上拉,而背板则将相应的信号接地。

P1接口信号IPMB_SCL,IPMB_SDA,IPMB_PWR用来进行系统管理,包括适配板识别,环境控制和电压控制。P2也有相应的3个引脚C19/D19/E19当做非背板总线管理系统使用。IPMB_PWR背板走线载流能力至少100mA。

CPCI通过母板进行电源分配。主要信号包括5V,3.3V,±12V,V(I/O)和GND。V(I/O)的载流能力最小为4A。电源要去耦,最好一个引脚加一个去耦电容。供电可以用ATX电源供电。

还有一个可选的热插拔信号Healthy。这个信号需要在背板上连接一个0.01uF的电容到地。需要注意的是此信号槽与槽直接不共享,也就是此信号不要各个槽连到一起。

系统槽需要提供7个时钟信号,唯一的分配给7个外围插槽。时钟线不能被共享。且时钟线长度需在5300mil到7300mil之间。由于任意两个PCI设备间的时钟倾斜不能大于2ns,设计的时候时钟线需要等长。

如果系统时钟是66MHz,背板最多有5个插槽,一个系统槽,4个外围槽。同时66MHz时钟使能信号M66EN传送给所有的插槽。如果是33MHz系统时钟,此引脚接地。

66MHz的时钟信号类似于33MHz的时钟信号的设计。不过长度要求在6300mil±40mil。

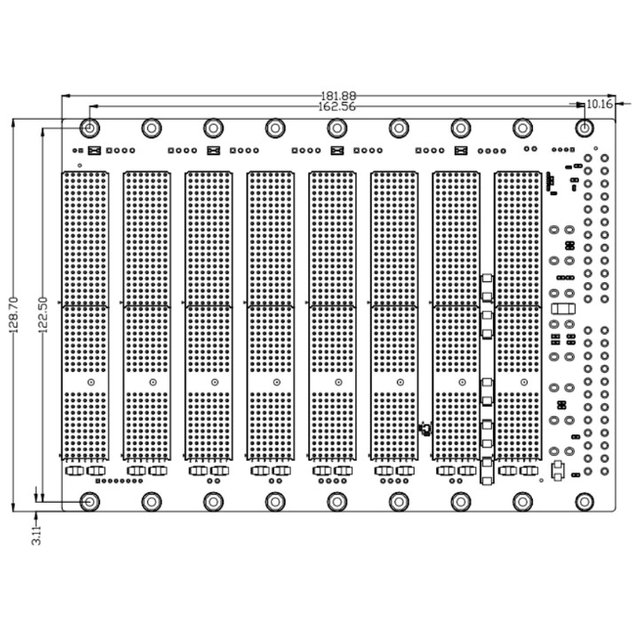

背板的机箱地与逻辑地要分离,通用方法是二者间接0.01uF电容进行交流耦合。关于背板尺寸可以参考图片。一般连接器前插板卡的前缀是J,底板前面的连接器是P,后插则分别是rP和rJ。

BRSVPxxx是预留的通信引脚,需要在连接器间互联。早期P1上的BRSVP1A5和BRSVP1B5被定义为SDONE#和SBO#。

对于热交换,还有一些长短脚的区别,比如D15引脚用作BD_SEL#信号,系统槽此信号接地的,不用于热交换外围槽也接地。对于热交换这里不细说。

不提倡使用JTAG信号。背板应将TCK,TMS,TRST#在各槽间互联。TDO和TDI可以悬空。

还有一个问题,REQ64#和ACK64#,当系统槽适配器为32位时必须提供上拉。我见过一种设计,系统槽母板上悬空。但是其它槽母板上直接上拉了。

其它信号各槽间共享。至于64位扩展信号,32位母板系统槽信号则直接忽略了,也就是悬空。我见过的一种设计只使用了系统槽后面板IO相关的一些信号。

[WhereIn Android] (http://www.wherein.io)

对于B列,除了B3,INTB#,遵循中断循环。B4,Healthy#,各槽分别接电容到地。B25,REQ64#,系统槽悬空,外围槽接VIO上拉。其余引脚均各槽间共享。

[WhereIn Android] (http://www.wherein.io)

👍🏻!shop

[WhereIn Android] (http://www.wherein.io)

谢谢

[WhereIn Android] (http://www.wherein.io)

👍

谢谢🥰

[WhereIn Android] (http://www.wherein.io)

This post has been rewarded by the Steem Community Curation Project #wherein

昨天明明把手机放在桌上,今天又找不到了 ( ˘︹˘ )

咦?你是谁?我又是谁?

加入我们微信群没?还没的话赶快加我们瓜子老板。很帅的 iguozi <(^,^)>

Ha recibido un voto a favor de la comunidad WHEREIN, impulsada por STEEMIT INC. Gracias por usar WHEREIN

Terimakasih Sudah Menggunakan WhereIn, Postingan Anda Terpilih Untuk Mendapatkan Upvote Dari WhereIn Dan Di Dukung Oleh Steemit.inc !

对于A列,A4,IPMB_PWR在各槽间共享。A6,为系统槽的REQ0#,为外围槽的REQ#,此信号是由系统槽分配过去的。所有的地址信号AD[31:0]在各槽间共享。C/BE[3:0]信号在各槽间共享。DEVSEL#,SERR#在各槽间共享。当然,电源也是共享的。

[WhereIn Android] (http://www.wherein.io)

你好鸭,lucienyong!

@boylikegirl给您叫了一份外卖!

南瓜糕点

吃饱了吗?跟我猜拳吧! 石头,剪刀,布~

如果您对我的服务满意,请不要吝啬您的点赞~

对于C列,除了INTC#遵循中断循环,其余信号均在各槽间共享。

[WhereIn Android] (http://www.wherein.io)

对于D列,D2 TDO信号在母板上悬空,D6对于系统槽而言,是CLK0,对于外围槽而言,则是系统槽分配的时钟信号。其余信号均在各槽间共享。

[WhereIn Android] (http://www.wherein.io)

对于E列,E2 TDI悬空;E3 INTD#遵循中断循环;E5对于系统槽而言是GNT0#,对于外围槽而言,则是系统槽分配的GNT#信号。对于E24而言ACK64#,系统槽悬空,外围槽2.7k上拉。其余信号各槽间共享。

[WhereIn Android] (http://www.wherein.io)

对于系统槽P2,用到了CLK,VIO,GND,REQ[x]#,GNT[x]#外,还有引出到外接口,不在槽间共享的FAL#,DEG#,PRST#信号以及GA[4:0]。其余信号均悬空。

[WhereIn Android] (http://www.wherein.io)