Betriebssysteme (6) - Hardware Interrupt

Für uns ist es störend, ständig bei der Arbeit unterbrochen zu werden. Für den Computer sind Unterbrechungen (interrupts) eine natürliche Form der Kommunikation.

Hardware-Unterbrechungen

Nehmen wir an, der Gerätetreiber einer Festplatte bekommt den Auftrag, einen bestimmten Block zu lesen. Der Gerätetreiber hinterlegt dafür einen entsprechenden Lesebefehl im Kontrollregister des Controllers. Der Controller kann jetzt mit seiner Arbeit beginnen. Aber wie erfährt die CPU davon, wenn der Leseauftrag ausgeführt ist und der gewünschte Block im internen Puffer des Controllers bereitliegt? Auf keinen Fall soll die schnelle CPU auf das langsame Gerät warten müssen. Zwei bessere Möglichkeiten bieten sich hierfür an:

polling : Die CPU kann immer wieder das Statusregister des Controllers abfragen, um festzustellen, ob der Auftrag schon erledigt ist. Allerdings wird bei einer erfolglosen Abfrage viel CPU-Zeit verbraucht

interrupt : Der Controller benachrichtigt die CPU, sobald er den Auftrag ausgeführt hat; hierzu unterbricht er die CPU bei ihrer augenblicklichen Arbeit. Dieser Unterbrechungsbetrieb bildet die Grundlage für die Arbeitsweise moderner Computersysteme.

Die CPU besitzt einen besonderen Eingang für Unterbrechungen. Jede Hardwarekomponente kann über den Bus ein binäres Signal an diesen Eingang legen. Entdeckt die CPU ein Unterbrechungssignal, rettet sie den Inhalt des Befehlszählregisters in einen systemeigenen Bereich des Hauptspeichers und lädt stattdessen die Anfangsadresse einer allgemeinen Prozedur zur Unterbrechungsbehandlung (interrupt handler). Diese stellt zunächst fest, welches Gerät die Unterbrechung auslösen will. Hierzu kann sie alle vorhandenen Geräte abfragen; in manchen Rechnern gibt es aber einen speziellen Unterbrechungs-Controller, der die Unterbrechungsanforderungen der Geräte verwaltet und ihre Herkunft kennt.

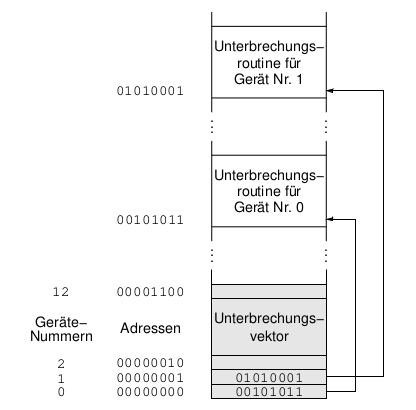

Die Nummer i des Geräts, das die Unterbrechung wünscht, wird nun als Index für den Unterbrechungsvektor verwendet. Dieser steht als

array[0 ... MaxDeviceNumber] of address

im systemeigenen Speicher und enthält an Position i die Startadresse der speziellen Unterbrechungsroutine für Gerät Nummer i.

Ein Unterbrechungsvektor

Diese Adresse wird in das Befehlszählregister geladen, und die spezielle Unterbrechungsroutine (interrupt service routine) wird gestartet. Da der Unterbrechungsvektor und die Unterbrechungsroutinen ein Bestandteil des Betriebssystems sind, wird das Betriebssystem durch die Ausführung einer Unterbrechungsroutine aktiviert, die wieder durch eine Unterbrechung aktiviert wird. Im Grund ist die Unterbrechung ein Mechanismus, das Betriebssystem zu aktivieren, dadurch übernimmt das Betriebssystem die Kontrolle über die CPU.

Wenn die Unterbrechungsroutine für ihre Arbeit längere Berechnungen anstellen muss, so werden zuvor auch die Registerinhalte der CPU in den systemeigenen Speicher gerettet, der meist als Stapel (stack) organisiert ist.

Die Unterbrechungsroutine hat die Aufgabe, den Unterbrechungswunsch des Geräts zu bearbeiten: Sie kann zum Beispiel den Gerätetreiber darüber informieren, dass der Controller seinen Lesebefehl ausgeführt hat und die Daten nunmehr bereitstehen.

Sobald die Unterbrechungsroutine ihre Arbeit beendet hat, wird zunächst ein spezieller Befehl ausgeführt, der die Rückkehr von der Unterbrechung (return from interrupt) bewirkt; vorher werden die alten Registerinhalte und der alte Wert des Befehlszählregisters wiederhergestellt. Dann kann die CPU mit ihrer unterbrochenen Arbeit fortfahren.

Mehrere Hardware-Unterbrechungen gleichzeitig

Es kann vorkommen, dass während der Bearbeitung einer Unterbrechung ein weiterer Unterbrechungswunsch eintrifft. Zur Vermeidung eines Durcheinanders sind verschiedene Maßnahmen möglich.

Zum einen lässt sich bei vielen Prozessoren der Unterbrechungseingang vorübergehend außer Betrieb setzen (interrupt disabled), so dass weitere Unterbrechungssignale wirkungslos bleiben.

So kann die CPU die zuerst eingetroffene Unterbrechung ungestört bearbeiten. Dieses Verfahren bietet sich auch in anderen Situationen an, wenn die CPU bei der Ausführung kritischer Abschnitte (näheres in einem der nächsten Beiträge) eines Programms nicht unterbrochen werden darf.

Zum anderen kann man jedem Unterbrechungswunsch eine Priorität zuordnen; Unterbrechungen niederer Priorität können dann von solchen mit höherer Priorität unterbrochen werden.

Jetzt haben wir gesehen, dass Geräte-Controller Unterbrechungen der CPU auslösen, wenn sie ihren Auftrag ausgeführt haben oder wenn ein Fehler aufgetreten ist. Da die Geräte-Controller, also ein Stück hardware, diese Unterbrechungen auslösen heißen diese Unterbrechungen hardware interrupts.

Quelle

Ayehsa, Saleem et. al. Review: Interrupt. In: I.J. Information Technology and Computer Science. 2018. DOI: 10.5815/ijser.2018.04.01

Alles richtig gemacht, weiter viel Erfolg...

Du hast ein kleines Upvote vom German-Steem-Bootcamp erhalten.

Du findest uns im Discord unter https://discord.gg/HVh2X9B

Aktueller Kurator ist @don-thomas

N E U - jeden Donnerstag findet bei uns ab 19 Uhr die Quasselstunde statt wo du nicht nur mit uns reden kannst - es werden auch tolle Preise verlost

Du möchtest keine Upvotes (mehr) von uns erhalten? Eine kurze Mittelung unter diesen Kommentar reicht.

Dem Upvote von uns folgt ein Trail der weitere Upvotes von unseren Unterstützern beinhaltet. Hier kannst du sehen wer diese sind und auch erfahren wie auch du uns und somit die deutschsprachige Community unterstützen kannst.

This post has been voted on by the SteemSTEM curation team and voting trail. It is elligible for support from @curie and @minnowbooster.

If you appreciate the work we are doing, then consider supporting our witness @stem.witness. Additional witness support to the curie witness would be appreciated as well.

For additional information please join us on the SteemSTEM discord and to get to know the rest of the community!

Please consider using the steemstem.io app and/or including @steemstem in the list of beneficiaries of this post. This could yield a stronger support from SteemSTEM.

@tipu curate

Upvoted 👌 (Mana: 10/20)

Congratulations @ozelot47! You have completed the following achievement on the Steem blockchain and have been rewarded with new badge(s) :

You can view your badges on your Steem Board and compare to others on the Steem Ranking

If you no longer want to receive notifications, reply to this comment with the word

STOPTo support your work, I also upvoted your post!

Hallo ich bin Mikrobi,

dein Beitrag hat mir sehr gut gefallen und du bekommst von mir Upvote.

Ich bin ein Testbot, wenn ich alles richtig gemacht habe, findest du deinen Beitrag in meinem Report wieder.

LG

Mikrobi