The future Blockchain node FPGA platform

The creation of a #NODE ON #BLOCKCHAIN IMPLEMENTED @FPGA @MODLTOKEN @MIBCOIN #SMARTHASH

Currently in the process creating and node so so many different platforms. Blockchain prototype that I'm working on implement first and foremost fpga platform which ability to do on the Fly programming with fpga platform. Fpga platform is the basis of the node. Within do you know the https://www.multichain.com/

MultiChain | Open source blockchain platform.

A Stratix IV FPGA from Altera

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence "field-programmable". The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an application-specific integrated circuit (ASIC) (circuit diagrams were previously used to specify the configuration, as they were for ASICs, but this is increasingly rare).

A Spartan FPGA from Xilinx

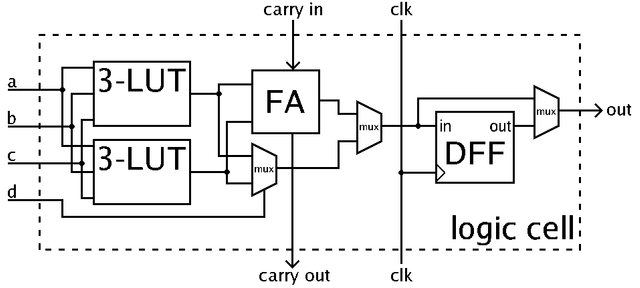

FPGAs contain an array of programmable logic blocks, and a hierarchy of reconfigurable interconnects that allow the blocks to be "wired together", like many logic gates that can be inter-wired in different configurations. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory.

Contemporary field-programmable gate arrays (FPGAs) have large resources of logic gates and RAM blocks to implement complex digital computations. As FPGA designs employ very fast I/O rates and bidirectional data buses, it becomes a challenge to verify correct timing of valid data within setup time and hold time. Floor planning enables resource allocation within FPGAs to meet these time constraints. FPGAs can be used to implement any logical function that an ASIC could perform. The ability to update the functionality after shipping, partial re-configuration of a portion of the design[2] and the low non-recurring engineering costs relative to an ASIC design (notwithstanding the generally higher unit cost), offer advantages for many applications.

The increase of logic in an FPGA has enabled larger and more complex algorithms to be programmed into the FPGA. The attachment of such an FPGA to a modern CPU over a high speed bus, like PCI express, has enabled the configurable logic to act more like a coprocessor rather than a peripheral. This has brought reconfigurable computing into the high-performance computing sphere.

Furthermore, by replicating an algorithm on an FPGA or the use of a multiplicity of FPGAs has enabled reconfigurable SIMD systems to be produced where several computational devices can concurrently operate on different data, which is highly parallel computing.

This heterogeneous systems technique is used in computing research and especially in supercomputing.[13] A 2008 paper reported speed-up factors of more than 4 orders of magnitude and energy saving factors by up to almost 4 orders of magnitude.[14] Some supercomputer firms offer heterogeneous processing blocks including FPGAs as accelerators.

This platform is 800 times the power of a basic C Code PC. Plus it is programmable on the fly. Creation of programmers such as the QR or barcode creation a device with a open source Linux kernel could change the algorithm instantly to adapt to the changes in any blockchain from Forks to algorithm changes implemented to accommodate companies like @Bitmain. @Intel #FPGA is all made in the USA.

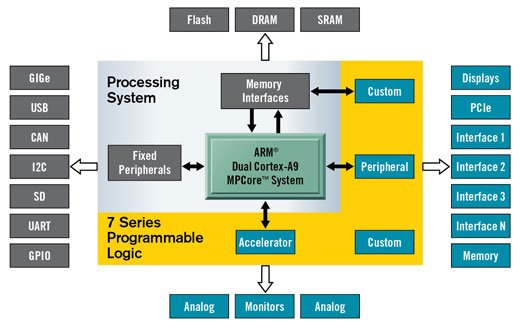

High-Performance Reconfigurable Computing (HPRC) is a computer architecture combining reconfigurable computing-based accelerators like field-programmable gate array with CPUs or multi-core processors.

The increase of logic in an FPGA has enabled larger and more complex algorithms to be programmed into the FPGA. The attachment of such an FPGA to a modern CPU over a high speed bus, like PCI express, has enabled the configurable logic to act more like a coprocessor rather than a peripheral. This has brought reconfigurable computing into the high-performance computing sphere.

Furthermore, by replicating an algorithm on an FPGA or the use of a multiplicity of FPGAs has enabled reconfigurable SIMD systems to be produced where several computational devices can concurrently operate on different data, which is highly parallel computing.

This heterogeneous systems technique is used in computing research and especially in supercomputing. A 2008 paper reported speed-up factors of more than 4 orders of magnitude and energy saving factors by up to almost 4 orders of magnitude. Some supercomputer firms offer heterogeneous processing blocks including FPGAs as accelerators.[citation needed] One research area is the twin-paradigm programming tool flow productivity obtained for such heterogeneous systems.

The US National Science Foundation has a center for high-performance reconfigurable computing (CHREC). In April 2011 the fourth Many-core and Reconfigurable Supercomputing Conference was held in Europe.

Commercial high-performance reconfigurable computing systems are beginning to emerge with the announcement of IBM integrating FPGAs with its POWER processor.

Partial re-configuration is the process of changing a portion of reconfigurable hardware circuitry while the other part is still running/operating. Field programmable gate arrays are often used as a support to partial reconfiguration.

Electronic hardware, like software, can be designed modularly, by creating subcomponents and then higher-level components to instantiate them. In many cases it is useful to be able to swap out one or several of these subcomponents while the FPGA is still operating.

Normally, reconfiguring an FPGA requires it to be held in reset while an external controller reloads a design onto it. Partial reconfiguration allows for critical parts of the design to continue operating while a controller either on the FPGA or off of it loads a partial design into a reconfigurable module. Partial reconfiguration also can be used to save space for multiple designs by only storing the partial designs that change between designs.

A common example for when partial reconfiguration would be useful is the case of a communication device. If the device is controlling multiple connections, some of which require encryption, it would be useful to be able to load different encryption cores without bringing the whole controller down.

Partial reconfiguration is not supported on all FPGAs. A special software flow with emphasis on modular design is required. Typically the design modules are built along well defined boundaries inside the FPGA that require the design to be specially mapped to the internal hardware.

From the functionality of the design, partial reconfiguration can be divided into two groups:

dynamic partial reconfiguration, also known as an active partial reconfiguration - permits to change the part of the device while the rest of an FPGA is still running;

static partial reconfiguration - the device is not active during the reconfiguration process. While the partial data is sent into the FPGA, the rest of the device is stopped (in the shutdown mode) and brought up after the configuration is completed.

This is the foundation of my PROTOTYPE.

This is only the beginning I have put in for a technical Grant and awaiting approval.

This foundation will bring forth capabilities unheard of and cripple the ASIC @Bitmain centralized Monopoly of the Cryptocurrency market and the semi conductor as well as the printed circuit board industry which will soon be brought back to the United States no of America because we are sovereign humans not commodity to be traded for debt when you the CIA has fully taken control by recruitment of your friends in the military industrial complex after getting your civilian papers creating a company funded by our tax dollars and other deepstate programs from gun running to drug running mainly to the mena Arkansas Airport under the control of the Clowns in America. @Cerco @D-wave 4096 running a world simulation at @CERN. THE FPGA IS JUST AS POWERFUL BUT THE COST FOR THE CHIPSET PLATFORM IS 11 THOUSAND INSTEAD OF 15 MILLION LIKE D-WAVE.

This is the important aspect IMPLEMENTATION of gpu FPGA chipsets into compatible cpu such as @Intel's @Xenon cpu.

Mitrionics has developed a SDK that enables software written using a single assignment language to be compiled and executed on FPGA-based computers. The Mitrion-C software language and Mitrion processor enable software developers to write and execute applications on FPGA-based computers in the same manner as with other computing technologies, such as graphical processing units (“GPUs”), cell-based processors, parallel processing units (“PPUs”), multi-core CPUs, and traditional single-core CPU clusters.

About the Mitrion-C Open Bio Project The Mitrion Virtual Processor

The purpose of the Mitrion-C Open Bio Project is to accelerate key bioinformatics applications by porting their performance critical parts to Mitrion-C and running these on the Mitrion Virtual Processor in FPGAs.

The first bioinformatics application that has been developed by the Mitrion-C Open Bio Project is a version of NCBI BLAST with an accelerated BLASTN program for nucleotide searches. Currently, the project is working on porting the BLASTP protein search algorithm to Mitrion-C.

The initial port of BLASTN has been done by Mitrionics with SGI contributing integration work for the SGI RASC RC100 platform.

The Mitrion Virtual Processor is a fine-grained, massively parallel, configurable soft-core processor that allows software to execute on FPGAs, without the software developer having to deal with the hardware desing tool complexities of working directly with the FPGA hardware.

Downloads Turn-key Version Development Tools

All relevant project files are at SourceForge.

If you need to get started with accelerated BLAST searches right away, Mitrionics is providing turn-key packages based on the project.

Mitrion-C development is done using the Mitrion Software Development Kit. Register on the My Mitrion user forum to get a free version.

Intel supports partial reconfiguration of their FPGA devices on 28 nm devices such as Stratix V, and on the 20 nm Arria 10 devices.The Intel FPGA partial reconfiguration flow for Arria 10 is based on the hierarchical design methodology in the Quartus Prime Pro software where users create physical partitions of the FPGA that can be reconfigured at runtime while the remainder of the design continues to operate. The Quartus Prime Pro software also support hierarchical partial reconfiguration and simulation of partial reconfiguration.

The flexibility in reconfigurable devices mainly comes from their routing interconnect. One style of interconnect made popular by FPGAs vendors, Xilinx and Altera are the island style layout, where blocks are arranged in an array with vertical and horizontal routing. A layout with inadequate routing may suffer from poor flexibility and resource utilisation, therefore providing limited performance. If too much interconnect is provided this requires more transistors than necessary and thus more silicon area, longer wires and more power consumption.

Challenges for operating systems Edit

One of the key challenges for reconfigurable computing is to enable higher design productivity and a more easy way to use reconfigurable computing systems for users that are unfamiliar with the underlying concepts. One way of doing this is to provide standardization and abstraction, usually supported and enforced by an operating system.[27]

One of the major tasks of an operating system is to hide the hardware and present programs (and their programmers) with nice, clean, elegant, and consistent abstractions to work with instead. In other words, the two main tasks of an operating system are abstraction and resource management.[27]

Abstraction is a powerful mechanism to handle complex and different (hardware) tasks in a well-defined and common manner. One of the most elementary OS abstractions is a process. A process is a running application that has the perception (provided by the OS) that it is running on its own on the underlying virtual hardware. This can be relaxed by the concept of threads, allowing different tasks to run concurrently on this virtual hardware to exploit task level parallelism. To allow different processes and threads to coordinate their work, communication and synchronization methods have to be provided by the OS.[27]

In addition to abstraction, resource management of the underlying hardware components is necessary because the virtual computers provided to the processes and threads by the operating system need to share available physical resources (processors, memory, and devices) spatially and temporarily.

Linux resolves this issue due to open-source and @linus being a part.

My plan is to continue to research #FPGA AND create a on the fly programmable CHIPSET to allow the control and true decentralization of the Blockchain and eliminate the ASIC platform along with the 90% control China has over this platform and every retail market in the US. @RealDonaldTrump this is where the power lies in today's technical world where cyber warfare has been a battle I was on the front lines risking my life by making videos through my research until all the sudden the narrative control changed. The same day after sitting demonetized for 8 months due to my upfront Barr nine fade all perception I was in the rabbit hole quiet as a mouse. I again want to thank you for reaching out personally for me to the Social Security main office in Montgomery AL.

@qanon1111 on @github

Http://steemit.com/@qanon1111

Http://drive.io/@qanon1111

Http://YouTube.com./c/vcchisolmfollowthewhiterabbit

Twitter

Http://twitter.com/austinyeshua

This prototype is covered under creative commons non commercial license.

Intel's public PGP KEY

Search Button

PGP Public Key

The latest security information on Intel® products.

Report a Vulnerability Product Support

PGP Public Keys

Use the Intel Product Security Incident Response Team public PGP key to encrypt email with sensitive information and to verify that security communications sent by Intel are genuine.

Active Date: Jul 6, 2018

Expiration Date: Jul 6, 2019

Key ID: 0x88F246DD

Key Type: RSA

Key Size: 4096/4096

Finger Print: 173A F58E 38C1 F5EE 99F9 8822 D31B 8B1E 88F2 46DD

User ID: [email protected]

You can download this key or copy-and-paste the text below.

-----BEGIN PGP PUBLIC KEY BLOCK-----

Version: Encryption Desktop 10.3.2 (Build 21165)

mQINBFs/rM4BEAC8zV5T4PqgnwZyU87RPWbSDFf7rzfnclIF+vR7oWUMc/xQTppz

qnHMyv9/r60uafFiIYCOcfSLUFLg9ROazRzZPNbDu8iG6DlMXUUwpHXIGcp0Swrf

4F9iPt69E3sPY+MyKz4/gjjH1KuupmpXRD07Q09byYWDOHfmvDmBUFz5e3qGCpNi

7h3eRKcJ8+gSeHbswTyHh2VSaS1u0uRsqVjzszwGz9b1oUeGmmn5A/NxenCfDqQD

874tXi0F2UDBqbiKe/NLYM4JV6UI7JyMV7ZWVjyq6ZYpECPMyuDB7oqq4vQN0ffO

awVHCV9nCYGAVqG+JikVvBOFPRnYeRgllyZLvNI+oXsCvyTyb1Ya04IC1B6KuNzL

i/1uHkOD0VJqNqX7RcuRjIWPXIU9YS4FtZhVaE1uNe6SuXMwjhwazG25pCUc6FLN

bOH1gK/d3WkD9m9FOGxUlwBowF19FkRtzgLqwBKKcDMlPtB+pEqbyL3MKyYVX0Ba

0w/dnr+DK5jC/Sq39CuIVZ+gVM2xVuD92Ep/UG908zB8xeUjB8y3lxBhth0e4Z3a

DGGWI4ZXw2Eh7G2y9fBso4cnrj2skocm39qRZp9RKp7E/tj2Tlj59sR3cPp6h9Db

tQoXi7dWG0bcWpgnv/KF+lncdq6yn2VIrzdW3TQW6he7bZ6+2fzH+lrVMQARAQAB

tEFJbnRlbCBQcm9kdWN0IFNlY3VyaXR5IEluY2lkZW50IFJlc3BvbnNlIFRlYW0g

IDxzZWN1cmVAaW50ZWwuY29tPokCeAQQAQIAYgUCWz+szgUJAeEzgDAUgAAAAAAg

AAdwcmVmZXJyZWQtZW1haWwtZW5jb2RpbmdAcGdwLmNvbXBncG1pbWUICwkIBwMC

AQoCGQEFGwMAAAAFFgADAgEFHgEAAAAGFQgJCgMCAAoJENMbix6I8kbdonIP/iDx

1TP/8v6Yyg/Y6Tmsv7tN1L4l7YwpprPhHL55WufwxvW+gH9/PqdVbmn0Q9BOqwk2

GfW2Ayc/D6ApTnSHy3VtNCObluNL0AqPJW0sGwwhjLmzhKskY5xSpXhMyMkAQwRc

1gH3lPPUWwQdaTZRI/Tf/fcLiXcmyvRxGuW0ZFj3jP+7Do6DmZ3/ESukDH2l0zHW

Vq2bu3Xu8qDL5QHSxH9klAMdH6aa/dtrUoC2ckfz3C60wZmcQwvpWp/+JSsXvpT+

UTYgpLBoqFbpHouM599mOmzDaXVod4oEVVO0RMNOHnX5kvYZQrOiFvGnV+oUcU9/

0QrjcXX2GDTZFWIYkHr8Dn0nIQ+AraGO8te0v4EQTwjGvqtm/ZX9yXI8enUBv3NS

A8RiVKx1DxvETDhVRv1tYzR0BMbhLaFplty42G9T6MYGR4etLbKMiAhcAMxNX8Au

ORuXC9ue69cNVi+rWm1MP8snpm8D+xljHKfLL/lO0crCiGiO49UXfhhvSpwgM2yl

izHf6Kx5TaIhlSX1loOEaYhKTTt7CxiOuu6JBlO4ocFnHzh8kZuhVCuyrBsGTrZS

Q/LIBBWv52ETGk3e15msFkNQqSHyEvq2A4Mz7fPtDgQG95vXJYWqZukhcsuoQFaN

p22y6yDB4NS0A6OVqWHGTbmBJqEYB5RQDyTwFvAVuQINBFs/rNEBEADpJm/VqKCu

TnDMEXTVjghotTvE4nOuijSzg2yQ6VnK1Yw1oSMzae2uC7HomFRE/zz7xxiuWIad

TB2e1brmJWnKfTWgcWt5mkTPWYNF6xkOSAy2DEBX/bPeCEcKJXlsC5I8wnTS+Gtb

TOoX6wzLn5teWkVctzk0OzRj8yj8aVES84MI37NlWO+VOoaprUruQVsDM1YD7WDS

PBWDmGYtXZ5clA46vETkn5iVil4pL8XdIfIYKRe0AANvYXtuDJWQ2VuR3kxzatkk

WJkNT+2LOdzltww1bIFgi/23tQRg9qwQEy9eHnSXq9mPVTkZOvatA4RyUfHAkV2q

Rkua5jAJfGOTqH2ORqHUB7aQVEBvKDNNzPUO2SZBoxgSQpIF5vY4h6eUmcCAnhNZ

CbVdcMCxCLKFSxkBPYcn8uZ6wUG0b/HMrXrh/qvCojxCCIj/0+zadXPNPHJYgvqV

O/AAO0IQfvSTt+knMDGaoTc+mvNoSISo+rsWZQdOt0oru9FoLqTCAgWSnnjWoYZs

NUX1z6X6+OSIBUvvb33GiUOK2zsGNJHsiFiOtu8aIVYQ2zY1vvRGS4WyQ/CA9snw

OYCYzk1qvGG4b6FpSQBJWFLE4juv8/5pXbSQoj3d5CDvM3zFxuo86hmnyvb/TAMS

HKxEBXnBoZNUOtymHra85fs6Dw1yty28hQARAQABiQRHBBgBAgIxBQJbP6zSBQkB

4TOABRsMAAAAwV0gBBkBCAAGBQJbP6zRAAoJEKCPoyACGUrX+1gP+gJ6LSzN3FrI

gV7ssVJWpthCiNyvaGi0SSFmdjwCLCeinCIGk53+EP9qZ34xTKBdr62Ydtir1an7

HxOerD/QrbXIIZX9FfwrPnuQhl74ApwFJSYuFyCpOOYryhk9GvpH6eFWJc/xk7kr

bOOnOy7dg35vOyZVz3QTDSQ7gb23yhpXR5LPMdCGtx4MwWgkIpDazy8Ar+OKZDRq

0Yp5hN9PrPiM2vooCuExfPX6xhkJoZHfxtnofNIm7tiUXcEoCM5TUVZsZIl2SOvL

FPuWHUsfOFFVwJCgBAqmrB1UOhZ463+JuNkSUD4xuH8XGu3EhJ9NRKr9AWJvnQc/

Z5u3bmFP2FbE3jwqE+6E6I+h6vqUp1W7Whp/dYsTF6aTrgfyIbZQFPvbjW+tSk9Q

pZwFH9IvSOz5sh30MkWlmr1oNhxICJ03bGhnxUKOySHMUV87ovZyZjE5xTNurLN4

6uRxVbE/afXtNn8ckfWv3y1VJn+bQQ0QN/TmhbUUKocbWAAti98QffjxVvou20YE

nJjvN4wPw0UZ3iT5u9iU/JVa1rm238AiBaXUc97ZiIIx2CIHMqrcgUW281RMyDfX

gOYAUMAP/MXAtCyDWSZSbnZYbkrGoS+SOWC3BS7VlB08f422gCKytDe9RKae6vgp

L4bTJco95ZjZIdh3gbUs9UvcRxQD6zBDAAoJENMbix6I8kbdj5UQALI71EuoqkER

UWwA3BepcrGizuLtuG8A3sHri0qSN/UHlEL2V1ejWKo7BaCal4csbIoNwzSIGVYt

88JG1/s5CRrBCySOtdYl9Sg4HeTe2F6TMx78wDAPjey8rFutHiKf3Mec7xzGsmT2

jEzukY1AyZ6nzoG+4Ilb1H3ldMWuFv5T5at13S8lhhBfYcvobIlfNB5ck0VTrwcX

QpeLWJzXgrNJY4lN78wbXcDnqquUc3nKY4TAi+SDhFLKh4UOTxdo8DujxWIO9yUr

qQ4zhHCyx+GynKPTJw8xaXEtIZy8ts9H+iErIACeNyC1LMxndJ0cuxN5HhzqH1/1

TTUoARgPek03tM6HRr+YD2SSukL26QzLg4ji7t0icSY7jUlZtBjDfUoOWKMULy04

SToIwcM1ZI1F20QusuHVUHo7Lolokhtn7lsCnBiJNhrplmu29hbTethQrM4jFzdf

/ly/5e419OLPldel9vpyEKN2fj1zlWjpdTFw6dzwhx2hoFxTmc4V76mpyYzKlzIH

fGgDOvgXrEPXHTaJqkxn+66t3SkQ1Tvm9KurH5pcQ+jYZIUgp6F7LCaAhNtdY++P

k0ZKeViIvQ54VLL/B3JbjzZx7tY3CX8If6umWBgnxXoKivoA681XlRixORlDrBVw

m6DhXS1uGaJ9pz/UoN4bYxKr588YHsi3

=T/YP

-----END PGP PUBLIC KEY BLOCK-----

TAGS: #fpga, azure microsoft so, blockchain, fpga, iot, mibcoin.io, mibpool, modltoken, module blockchain, platform node, protype platform node, zo

Hi @qanon1111, I'm @checky ! While checking the mentions made in this post I noticed that @fpga, @mibcoin and @cerco don't exist on Steem. Did you mean to write @pgr, @bitcoin and @ceyco ?

If you found this comment useful, consider upvoting it to help keep this bot running. You can see a list of all available commands by replying with

!help.@checky follow me